光電半導體類 110 專研專刊

## 硼掺雜氧化鋅透明薄膜之特性研究

系所/電子工程學系 指導老師/邱福千 組員/洪珮倫、湯妙行、陳亭佑、謝佳紜

電阻式記憶體(Resistive Random-Access Memory, RRAM)技術是現在非揮發性記憶體新技術中最具有潛力的,其擁有高運算速度、低操作功耗、體積小、耐久度佳等,並與CMOS有良好的相容性。

氧化鋅(Zinc Oxide)具有寬能隙、無 毒性、資源豐富等特性。而純氧化鋅薄 膜實為高電阻率的半導體材料,可藉由 摻雜其他元素來提升導電率,常見的元 素有硼(B)、鋁(Al)、氮(N)、磷(P)、砷 (As)等元素,摻雜也可以使氧化鋅具有 P型或 N型半導體性質,結合這二種型 態可製作出 P-N 接面半導體元件。

RRAM 具有兩種不同的電阻狀態,分為高電阻態(HRS)和低電阻態(LRS)。當元件從 HRS 轉變為 LRS,稱之為設置(Set)過程,從 LRS 轉變為HRS,稱之為重置(Reset)過程。RRAM的寫入與抹除是透過循環操作 Set 與Reset 步驟來達成。

本 實 驗 中 採 用

Ni(60nm)/ZnO:B(23.5nm)/Ni(263nm)

MIM 結構的電容器。其中 ZnO:B 薄膜

在可見光範圍內的穿透率平均高達 91.86%;能隙為3.22 eV。

圖 1: Ni/ZnO:B/Ni 元件結構圖

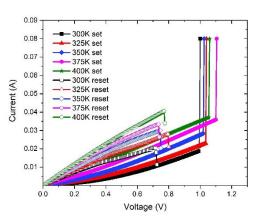

電性量測方面,先設置 50mA 的限制電流,再藉由電壓掃描 (Voltage Sweep)法量測 ZnO:B 薄膜元件的電流電壓特性曲線(I-V Curve),如圖 2 所示,可觀察到元件初始阻態為 HRS,且不需經過 Forming 即可具備記憶體元件的電阻轉換特性。此元件只能在正偏壓下做 Set 與 Reset 的動作,這也表示其為單極性元件。

圖 2:300K 到 400K 時 HRS 與 LRS 的電流對電壓關係圖

## 光電半導體類

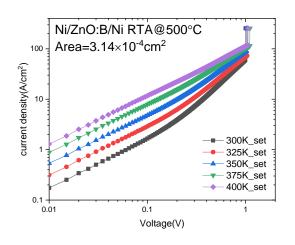

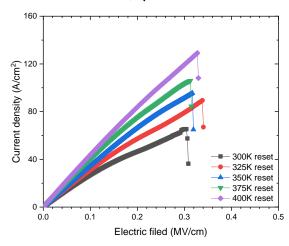

接著我們對元件做傳導機制的分析,圖 3 為高阻態時在 300K 到 400K 的電流-電壓曲線,可以看到溫度為 300K 時為空間電荷限制傳導(SCLC),但是隨著溫度的上升,V > Vtr 範圍的斜率漸漸趨近於 1,直到溫度為 400K 時斜率為 1,也就是說隨著溫度上升,傳導機制會由 SCLC 逐漸變為歐姆傳導。在低阻態時,從圖 4 中發現電壓電流曲線呈線性關係,所以我們判斷在低阻態時的電流傳導機制為歐姆傳導。

圖 3: HRS 在溫度 300K- 400K 的 I-V 曲線

圖 4:LRS 在溫度 300K 至 400K 之歐姆 傳導分析圖

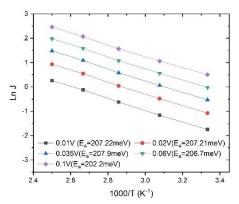

陷阱能階 $(E_c-E_t)$ 可以由 Arrhenius plot 求得,即在  $\ln(J)$ -1/T 的圖中,曲線 斜率為 $(E_t-E_c)/k$ 。而圖 5 為高阻態時 的 Arrhenius plot,利用此圖可以得到高阻態時活化能 $E_a=207 \text{meV}$ ,也就是說陷阱能階 $E_c-E_t=207 \text{meV}$ 。同樣地,也可以利用 Arrhenius plot 求得低阻態時的活化能 $E_a=49 \text{meV}$ 。

圖 5: HRS 時的 Arrhenius plot

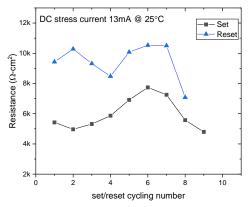

圖 6 為常溫下施加應力電流 13mA 時元件的循環容忍度測試圖。Set 的電 壓範圍落在 1 V-1.1 V,會使薄膜出現軟 崩潰(Soft Breakdown)的現象。從圖中可 以看到,在承受 13mA 的高電流後,會 導致薄膜退化,經過 6 次循環後會使得 薄膜轉變為硬崩潰(Hard Breakdown)。

圖 6:HRS/LRS 循環容忍度測試圖